荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

图片来源 / Unsplash

来源 / 荣格电子芯片编译自semiengineering

作者 / BRIAN BAILEY

定义 2.5D 器件是缩小以适合封装的印刷电路板,还是超出单个芯片限制的芯片,这似乎是令人吹毛求疵的语义,但它可能会对设计的整体成功产生重大影响。

平面芯片一直受到掩模版尺寸的限制,约为 858mm2。除此之外,良率问题使硅不经济。多年来,这限制了可以填充到平面基板上的特性数量。任何附加功能都需要设计成额外的芯片,并与印刷电路板 (PCB) 连接。

2.5D封装技术的出现开辟了一条全新的扩展轴,允许在先进的封装内互连多个小芯片。但是,这种打包设计的起点可能会对各种组件的组装方式、参与人员、部署哪些工具以及何时部署产生重大影响。

2.5D今天取得进展有几个原因。一是成本。“如果你能制造出更小的芯片或小芯片,并且这些小芯片经过设计和优化,可以集成到封装中,那么它可以使整个产品变得更小,”西门子数字工业软件先进封装解决方案总监 Tony Mastroianni 表示:“而且由于产量要高得多,这对成本产生了巨大影响。裸片尺寸芯片的良率不是 50% 或以下,而是可以达到 90% 的范围。”

使用 PCB 互连芯片也会限制性能。“从历史上看,我们的芯片是分开封装的,放在PCB上,并通过一些布线连接,”Eliyan的首席执行官兼联合创始人Ramin Farjadrad说。“人们开始面临的问题是双重的。一个是这些芯片之间的带宽通过PCB而受到限制,然后封装上有限数量的球限制了这些芯片之间的连接。”

与PCB相比,2.5D的主要区别在于2.5D使用芯片尺寸。有更细的颗粒线,各种组件可以在转接层或封装中比在电路板上更紧密地封装在一起。由于这些原因,电线可以更短,可以有更多,带宽也会增加。

这会影响多个级别的性能。“由于它们离得很近,因此没有长时间的运输RC或LC延迟,因此速度要快得多,”西门子的 Mastroianni 说。“你不需要芯片上的大驱动器来驱动电路板上的长走线,所以你的功耗更低。你可以获得数量级的性能提升和更低的功耗。一个常见的指标是谈论每比特的皮焦耳。移动比特所需的能量使2.5D引人注目。

尽管如此,这种思维方式仍然会影响最初的设计概念,并在整个流程中产生影响。“如果你和芯片设计师交谈,他们可能会说这只是一个大芯片,”Cadence定制集成电路和PCB组的产品管理组总监John Park说。“但如果你和包装设计师或电路板设计师谈话,他们会说这基本上是一个微型PCB。”

谁是对的?“公司内部的组织结构往往决定了如何处理这个问题。”Ansys产品营销总监Marc Swinnen说。“从长远来看,你要确保你的公司结构与物理学相匹配,而不是试图将物理学与你的公司相匹配。”

显而易见的是,没有什么是确定的。“数字世界非常规律,因为每两年我们就会得到一个一半大小的新节点,”Cadence's Park 说。“会有一些新的要求,但它是非常进化的。包装是狂野的西部。我们今年可能会获得 8 项新的包装技术,明年 3 项,明年 12 项。其中许多来自代工厂,而过去仅来自外包半导体组装和测试公司(OSAT)和基板供应商。虽然代工厂是新进入者,但OSAT正在以较低的成本提供一些非常有趣的封装技术。”

造成这种情况的部分原因是不同的人群有不同的需求。“政府和军方认为异构集成能力的主要好处是,”Ansys的Swinnen说。“他们没有推动加工技术的前沿。相反,他们正在设计单片微波集成电路(MMIC)之类的东西,他们需要波导来传输非常高速的信号。他们从包装组装的角度来处理它。相反,高性能计算 (HPC) 公司从一堆具有高性能高带宽内存 (HBM) 的 5nm 和 3nm 芯片中接近它。他们认为这是一个硅组装问题。他们看到的好处是架构的灵活性,他们可以投入内核和接口,并为特定市场创建产品,而无需重新设计每个小芯片。他们认为灵活性是好处。军方将异构集成视为优势。”

Part 1

材料

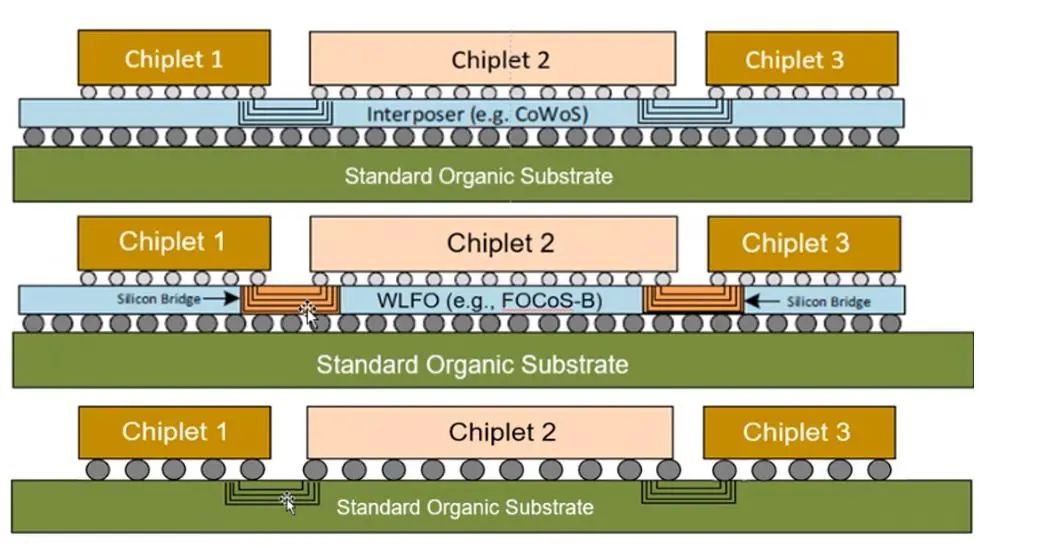

在2.5D封装技术中,有几种材料被用作基板,每种材料在成本、密度和带宽方面都有不同的权衡,并且每种材料都有必须克服的不同物理问题。主要的差异点之一是凸块间距,如图 1 所示。

图 1.用于各种基板配置的小芯片互连。资料来源:Eliyan

当谈到中介层时,它通常被认为是硅。“中介层可以是一大块硅(图1顶部),也可以只是芯片之间的硅桥(图1中间)以提供连接,”Eliyan的Farjadrad说。“这两种解决方案都使用高密度的微凸块。中介层和桥接器提供了大量高密度的凸点和迹线,从而为您提供了带宽。如果您使用 1,000 根电线,每根电线以5Gb的速度运行,您将获得5Tb。如果你有10,000个,你会得到 50Tb。但这些信号不能超过两三毫米。或者,如果避免使用硅中介层,而使用有机封装(图 1 底部),例如倒装芯片封装,则走线密度会降低5倍到10倍。但是,电线的厚度可以增加5到10倍。这是一个显着的优势,因为电线的电阻会随着电线粗细的平方而下降。该导线的横截面上升了该导线的平方,因此电阻显着下降。如果密度降低5倍,这意味着您可以将信号运行得再远近25倍。”

对于某些人来说,这一切都与每毫米的带宽有关。“如果你有一个并行总线,或者一个高速的并行接口,并且你想要每毫米带宽,那么你可能会选择硅中介层,”Synopsys解决方案集团硬件工程高级经理 Kent Stahn 说。“有机基材是低损耗、低成本的,但它没有密度。在这两者之间,有一堆解决方案可以满足其中的一些要求,但成本不同。”

选择基材还有其他原因。“硅中介层来自晶圆代工厂,因此可用性是一个问题,”Synopsys Solutions Group 高级产品经理 Manuel Mota 说。“一些公司在采购高级包装方面面临挑战,因为产能被占用。通过转到带宽密度稍低但可能足以满足您的应用程序的其他技术,您可以在其他地方找到它们。这正在成为一个关键方面。”

然而,所有这些技术都在迅速发展。“标线限制约为 858 平方毫米,”Park 说。“人们谈论的中介层可能是这个尺寸的四倍,但我们有更大的层压板。一些来自日本的层压基板正在接近我们从硅中获得的相同水平的互连密度。我个人认为,对有机基材的推动力更大。台积电的晶圆基板芯片 (CoWoS) 使用硅中介层,并且一直是大约 12 年来的首选技术。最近,他们推出了CoWoS-R,它使用薄膜聚酰胺,更接近有机类型的基材。现在我们听到了很多关于玻璃基板的信息。”

随着时间的流逝,包裹内的总空间可能会增长。“对于代工厂来说,继续制造30英寸印刷电路板大小的东西是没有意义的,”Park补充道。“有些材料能够解决更大的设计。我们真正需要密度的地方是死对死。我们希望这些小芯片彼此相邻,互连长度为几毫米。我们希望事情非常简短。但剩下的只是扇出 I/O,以便它连接到 PCB。”

这就是桥接受欢迎的原因。“我们确实看到了接口高速部分的桥接的发展,”Synopsys 的 Stahn 说。“它的背面将是扇出,就像 RDL 扇出一样。我们看到 RDL 封装未来将更像传统封装。”

中介层提供额外的功能。“今天,99%的中介层是无源的,”Park说。“没有生产线的前端,没有设备层。它纯粹是生产线处理的后端。你要在硅上添加三层、四层、五层金属层。这就是我们所说的无源中介层。它只是在创造这种 die-to-die 互连。但有些人把这个骰子变成一个活跃的中介层,基本上是给它增加了逻辑。”

这可能出于不同的目的而发生。“你已经看到一些公司在做有源中介层,他们增加了电源管理或一些控制逻辑,”Mota说。“当你开始在中介层上放置有源电路时,它仍然是 2.5D 积分,还是变成 3D 积分?我们今天没有看到有源中介层的大趋势。

不过,也有一些新问题。“你必须考虑热膨胀系数(CTE)失配,”Stahn说。“每当两种具有不同 CTE 的材料粘合在一起时,就会发生这种情况。让我们从硅中介层开始。您可以获得更高瓦数的系统,SoC 可以与同行通信,这可能会消耗大量功率。硅中介层仍然必须封装。CTE不匹配是硅与封装材料之间的不匹配。有了桥接器,你可以在你需要的地方使用它,但它仍然是硅芯片到芯片。您必须进行热机械分析,以确保您提供的功率和您拥有的 CTE 不匹配导致可行的系统。”

虽然理论上信号长度可以变长,但这会带来一些问题。“当你在芯片内部建立这些长连接时,你通常会将这些路由限制在几毫米以内,然后你缓冲它,”Mastroianni说。“无源硅中介层的问题在于没有缓冲器。这确实可能成为一个严重的问题。如果你确实需要建立这些连接,你需要非常仔细地计划这些连接。而且,您确实需要确保运行时序分析。通常,您的软件包人员不会进行该分析。这更像是硅工程师通过静态时序分析解决的问题。我们确实需要引入 STA 流程并处理所有包括有机和硅型迹线在内的提取,这成为一个新问题。当您开始进入一些非常长的走线时,在正常的STA延迟计算器中假设的简单RC定时延迟没有考虑到这些走线之间的一些电感和互感,因此您可能会遇到这些长走线的严重精度问题。

有源转接层会有所帮助。“使用有源中介层,您可以通过放置缓冲器或信号中继器来克服一些长距离问题,”Swinnen说。“然后它又开始看起来更像一个芯片,你只能在硅上做。你有英特尔的 EMIB 技术,他们将小芯片嵌入到中介层中,这是一个有源桥接器。芯片与EMIB芯片通信,它们都通过这个小的有源桥接芯片与你通信,它不完全是一个有源中介层,但几乎就像一个有源中介层。”

但即使是无源元件也能增加价值。“要做的第一件事是在中介层中包括沟槽电容器,”Mastroianni说。“这使你能够做一些很好的解耦,在关键的地方,靠近骰子。如果将它们放在电路板上,则会失去高速接口的很多好处。如果你能把它们放在中介层中,正好位于你有快速开关速度信号的地方,你就可以得到一些局部去耦。”

除了不同的材料外,还有一个问题,即谁设计了中介层。“在谁在进行设计的背景下,业界似乎将其视为一个小PCB,”Ansys产品管理高级经理Matt Commens说。“中介层通常由封装工程师设计,即使它们是硅工艺。对于高性能产品尤其如此。这似乎有悖常理,但他们有信号完整性的背景,他们一直在设计传输线,并最大限度地减少互连处的不匹配。传统的IC设计人员从组件的角度工作。所以可以肯定的是,这个行业告诉我们,他们指派去做这些设计工作的人是包装型的角色。”

Part 2

电源

PCB和中介层之间的布线存在相当大的差异。“与PCB相比,中介层布线要容易得多,因为组件数量大大减少,”Fraunhofer IIS/EAS高效电子部门负责人Andy Heinig说。“另一方面,由于金属层的电阻较高,并且电网被信号线切断,因此中介层上的电网要复杂得多。由于布线密度的原因,晶粒到晶粒接口的布线更加复杂。

电力输送看起来非常不同。“如果你看一个PCB,他们会把这些大的金属浇注区域嵌入层中,然后把它们排空出需要通过的区域,”Park说。“你放下一堆铜,然后你把其他的都排空了。我们不能以这种方式构建中介层。我们必须沉积互连,因此硅中介层上的电源和接地结构看起来更像数字芯片。但信号看起来更像是PCB或层压板封装。

布线看起来更像是PCB而不是芯片。“你会看到像泪滴或圆角这样的东西,它与垫子或通孔连接,以创造更好的产量,”Park补充道。“如今的布线方式更符合PCB,而不是数字IC,在数字IC中,你只有90°的正交角和干净的布线通道。对于中介层,无论是硅还是有机,过孔通常比导线大,这是一个典型的PCB问题。如果我们谈论的是数字路由器,那么路由器更像是一个小型PCB,而不是一个芯片。

TSV 也会产生问题。“如果你打算将它们视为正方形,那么你就会在拐角处失去大量空间,”Swinnen 说。“你确实希望这些物体周围呈 45°角。硅路由器传统上是曼哈顿式的,尽管 RDL 路由有着悠久的传统,RDL 路由是连接凸块的顶层。传统上使用八角形凸块或圆形凸块,然后进行 45°布线。它不像 PCB 布线那么灵活,但他们有重新分配层路由器,而且他们还有一些来自完全定制侧的路由器,具有完整的河流布线。”

原文链接:

https://semiengineering.com/2-5d-integration-big-chip-or-small-pcb/

注:Brian Bailey is Technology Editor/EDA for Semiconductor Engineering.

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。