荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

图片来源 / Intel

来源 / Semiwiki;荣格电子芯片翻译

作者 / Mike Gianfagna

#61DAC今年的讨论焦点是人工智能和多芯片、异构设计。让2.5/3D设计和chiplet生态系统成为主流现实的承诺是会议中许多小组讨论和演讲的焦点。

人工智能确实推动了这种新的设计风格的发展,但讨论的范围远不止人工智能,正如您将在下面看到的那样。这种新的设计风格需要半导体生态系统的每个部分的努力,而DAC期间的讨论清楚地展示了这一点。所有这些工作的交汇点是使之在商业上可行的焦点。这个焦点就是晶圆厂,在DAC的周二上午有一场精彩的主题演讲,详细解释了如何打开通往未来的大门。让我们来探讨一下英特尔的 Gary Patton 如何展示通往系统代工厂的道路。

Part 1

系统晶圆厂是什么,为什么它很重要

在我开始介绍Gary的主题演讲之前,我想先谈谈房间里的大象。我在半导体行业工作了很长时间。多年来,我把英特尔看作是一个技术巨头,主导市场,击败竞争对手,并以“英特尔方式”行事。

当我听到“英特尔”时,首先想到的不一定是开放、协作、以生态系统为中心和面向服务。但这正是盖瑞·帕顿博士(Dr. Gary Patton)在他的主题演讲中所传达的内容。显然,英特尔正在发生改变,而且是大刀阔斧的改变。通过其系统级封装(systems foundry)计划,英特尔正积极地在定义半导体设计和制造的未来方面发挥领导作用。这一角色需要一种新的企业文化,而Gary是英特尔高管中引领这一转变的人之一。我在DAC大会上与Gary进行了一对一的交流,接下来我将分享他的一些个人见解。但在此之前,让我们先来看看他演讲中的一些信息。

Gary从一些令人大开眼界的数据开始演讲。根据IDC的数据,世界每天产生近270万拍字节(petabytes)的数据。这是270,000,000,000千兆字节。英特尔预计到2030年,平均每位用户的计算能力将达到1拍字节(1,000,000,000,000,000,000次浮点运算),数据存储量将达到1拍字节(1,000,000,000,000,000,000字节),两者之间的距离将不到1毫秒。要实现这些目标,需要颠覆性的创新——这种创新显然超越了我们长期以来依赖的摩尔定律的规模。

他还提到,尽管人工智能正在推动数据量和数据处理需求的巨大增长,但它也带来了显著的能源效率挑战。据《纽约时报》和谷歌称,人工智能可能很快需要相当于一个国家(每年约100太瓦时)的电力。

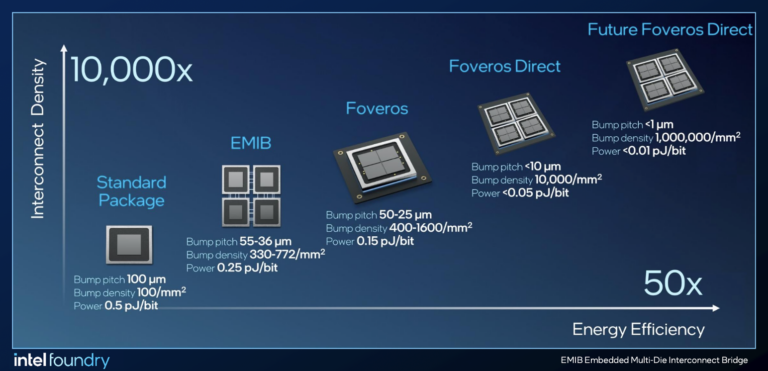

Gary指出,颠覆性创新对我们这个行业来说并不新鲜。多年来,我们已经克服了双极性功率限制、栅极氧化限制,以及现在的平面器件限制。要克服最后一个问题,就需要结合芯片和小芯片实现,以及封装互连密度和能源效率。英特尔的目标是成为所有这些创新的中心,这就是其“系统晶圆(Systems Foundry)”计划的宗旨所在。

得益于其先进的封装工作,英特尔有望实现 50 倍的能效提升和 10,000 倍的互连密度提升,如下图所示。

Part 2

英特尔封装创新

Gary不仅关注英特尔自身的创新,还对整个行业进行了深入的思考。他谈到了UCIe联盟的工作,该联盟由135家公司组成。该联盟的目标是开发一个开放的标准,定义芯片封装内的互联方式,从而建立一个开放的chiplet生态系统,并在封装层面实现无处不在的互联。Gary解释说,UCIe的工作与图中左下角的标准封装相比,在能效方面实现了两倍的提升,在带宽方面实现了三到四倍的提升。这些封装改进还实现了至少比外部互联(如PCIe、以太网等)低一个数量级的延迟。这是英特尔晶圆厂明确支持的重要工作。

Gary随后讨论了系统技术协同优化的重要性,这是一种更广泛、更雄心勃勃的设计技术协同优化。他解释说,软件和架构、封装和芯片都是这项工作的一部分,必须是整体的。他表示,“堆栈中各个层的进展是必要的,但还不够。整个系统必须进行协同优化。”

虽然英特尔的大部分先进工艺和封装工作都在推动这一努力,但与整个IP、EDA、设计服务和先进系统组装和测试生态系统的紧密合作对于成功同样至关重要。他详细介绍了英特尔晶圆厂与其生态系统合作伙伴开展的许多项目,以构建和认证下一代设计和制造能力。他描述了与所有关键 EDA 供应商的定期会议,并展示了所有关键英特尔技术的 EDA 认证非常详细的记分卡。这项工作的广度确实令人印象深刻。稍后将在本文中提供更多证据,证明英特尔致力于开放式设计流程。

Gary介绍了英特尔在五年内为实现系统级晶圆厂能力所做的投资。他报告称,目前该公司已有100多个2.5D设计投入生产。设计支持、开放和协作的态度、以质量为先的文化以及强大的客户支持和认证方法都是这一投资的一部分,如图所示。

英特尔投资

上图让我深刻认识到,这确实是一个全新的、改进后的英特尔公司。它保留了其在技术方面的优势,并增加了成为世界一流代工厂的所有要素,从而成为一个系统级代工厂。接下来,让我们认识一下主题演讲的主持人。

Part 3

引领变革——加里·帕顿的观点

加里·帕顿

在DAC大会上发表主题演讲后,我有幸与加里进行了私下交流。加里是英特尔在过去几年中聘请的众多“局外人”中的一员——上述五年投资计划中的一部分。我认为加里整个职业生涯的积累为他在英特尔的工作打下了坚实的基础。在斯坦福大学获得EE博士学位后,他在IBM担任过25年以上的领导职务,涉及研究、微电子以及各种企业项目和产品线。在此期间,他磨练了自己的产品/技术开发以及生态系统合作技能。

然后,他在格罗方德担任了4.5年的首席技术官和全球研发与设计支持高级副总裁。现在,他在英特尔担任4.5年的高级副总裁兼总经理,负责Foundry Design Enablement。他是英特尔众多最近招聘的员工之一,为公司带来了广泛的行业经验。

加里解释说,他对英特尔的成就一直怀有深深的敬意。他加入该公司不是为了“解决问题”,而是为了将一家伟大的公司提升到新的水平。看来一切都很顺利。他把过去的4.5年视为职业生涯中最好的时光。考虑到他所取得的成就,这可是很高的评价。

加里谈到了英特尔公司内部的一次转变,以应对即将到来的更广泛的挑战和机遇。高层的基调是其中的重要组成部分,帕特·格尔辛格(Pat Gelsinger)正是传达这些信息的合适人选。与加里交谈是一种乐趣。他口齿伶俐、平易近人,是一位非常有效的领导者。他最后说的一句话给我留下了深刻印象。他解释说,从之前的经历中他学到了很多东西,其中一个关键点是,“如果你从事铸造业,你的客户会让你变得更好。”

Part 4

证明:英特尔致力于开放的设计流程

在DAC的第一天,英特尔的生态系统合作伙伴宣布了一系列支持访问英特尔EMIB技术的举措,这进一步证明了英特尔不断扩大的生态系统以及对创建广泛参考流程的承诺。英特尔生态系统合作伙伴发布了以下公告,以支持访问英特尔的 EMIB 技术:

Ansys正在与Intel Foundry合作,为英特尔的EMIB技术提供全面的热力和功率完整性验证以及机械可靠性验证,该技术涵盖先进的硅工艺节点和各种异构封装平台。

Cadence 宣布推出完整的 EMIB 2.5D 封装流程、Intel 18A 的数字和定制/模拟流程,以及 Intel 18A 的设计 IP。

西门子宣布为 Intel Foundry 的客户提供 EMIB 参考流程。此外,他们还宣布获得 Solido™ Simulation Suite 认证,用于在 Intel 16、Intel 3 和 Intel 18A 节点上进行定制 IC 验证。

Synopsys 宣布推出其 AI 驱动的多芯片参考流程,用于 Intel Foundry 的 EMIB 先进封装技术,从而加速多芯片设计的开发。

Intel Foundry 生态系统开发副总裁 Suk Lee 评论道:“今天的新闻展示了 Intel Foundry 如何继续将英特尔的优点与我们生态系统的优点相结合,帮助我们的客户实现他们的 AI 系统抱负。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。