荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

日前,Geoffrey Yeap 博士在 IEDM 上展示了2nm平台技术,该技术具有与 3DIC 共同优化的 2nm 平台技术,用于 AI、HPC 和移动 SoC 应用。他是台积电研发先进技术的副总裁。Geoffrey 已在 TSMC 工作了近 9 年,还曾在 Qualcomm、Motorola Mobility、AMD 和德克萨斯大学超级计算系统中心领导高级工作。

Geoffrey 表示,自23年第一季度生成式 AI 取得突破以来,AI 与 5G 高级移动和 HPC 一起在半导体行业产生了对一流节能逻辑技术的巨大需求,而这项工作满足了这一需求。

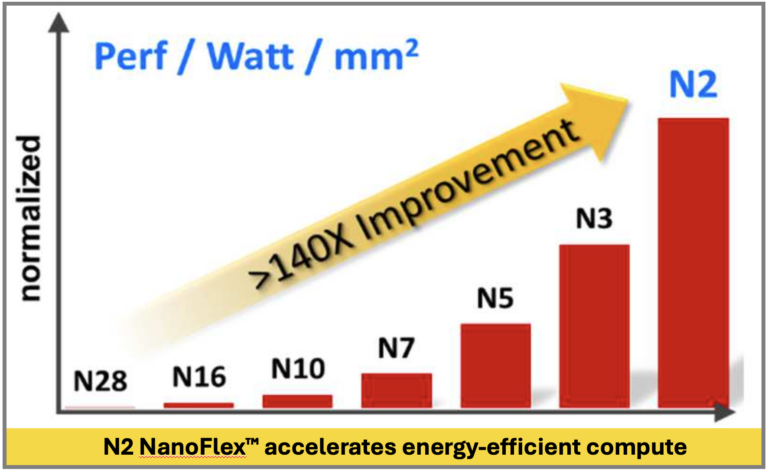

Geoffrey 描述了最先进的 TSMC N2 技术及其成功过渡到 NS 平台技术,将 28nm 到 N2 的节能计算速度提高了 >140 倍,如以下图表所示。N2 逻辑技术采用节能型全环绕栅极纳米片晶体管、中间线和后端互连,具有 ~38Mb/mm2 的最密集 SRAM 宏。N2 提供了比以前的 3nm 节点更丰富的节点优势,可提供 15% 的速度提升或 30% 的功耗降低,芯片密度提高了 >1.15 倍。

N2 平台技术配备了新的铜缆可扩展 RDL 互连、平坦钝化和 TSV。它与 TSMC 的 3DFabric™ 技术进行整体优化,为目标 AI/移动/HPC 产品设计提供系统集成/扩展。

Geoffrey 报告说,N2 已成功满足晶圆级可靠性要求,并通过了 1,000 小时的 HTOL 认证,具有高良率 256Mb HC/HD SRAM 和由 CPU/GPU/SoC 模块组成的逻辑测试芯片(>3B 门)。N2 目前正在进行风险生产。N2 平台技术计划于 2025 年下半年量产。N2P 是 N2 的 5% 速度增强版本,具有完全的 GDS 兼容性,计划于 2025 年完成认证,并于 2026 年投入量产。

从平台的角度来看,Geoffrey 提供了有关 N2 NanoFlex™ 技术架构的一些细节。系统技术协同优化 (STCO) 与智能缩放功能一起使用,而不是蛮力设计规则缩放,这可能会大大增加工艺成本,并在无意中导致严重的良率问题。在优化技术以实现目标 PPA 时,进行了广泛的 STCO 以及主要设计规则(例如栅极、纳米片、MoL、Cu RDL、钝化、TSV)的智能缩放。

他指出,与 3DFabric SoIC 3D 堆叠和先进封装技术(INFO/CoWoS 变体)的协同优化已经完成,从而加速了 AI/移动/HPC 产品设计的系统集成/扩展。N2 NanoFlex 标准单元创新不仅提供纳米片宽度调制,还提供备受期待的多单元架构设计灵活性。

此功能提供了 N2 短单元库,以提高面积和功率效率。他解释说,选择性使用 tall 单元库元件可以提高频率以满足设计目标。N2 具有 6 种 Vt 产品,频率范围为 200mV,可提供前所未有的设计灵活性,以最佳逻辑密度满足各种高能效计算应用的需求。下图说明了这种方法对基于 Arm 的设计的一些好处。

N2 NanoFlex HD 电池的优势

Geoffrey 解释说,在 0.5V- 0.6V 的低 Vdd 范围内,N2 纳米片技术的性能/瓦特比 FinFET 好得多。通过工艺和器件的持续改进,重点放在低 Vdd 性能/瓦特提升上,从而在 0.5V 运行时实现 20% 的速度提升和 75% 的待机功率降低。N2 NanoFlex 与 multi-Vt 相结合,提供了前所未有的设计灵活性,以最具竞争力的逻辑密度满足各种高能效计算应用。

Geoffrey 详细介绍了 SRAM、logic test chip 以及 qualification and reliability。这是一次令人印象深刻的演讲。N2 技术平台为未来的创新带来了许多新功能。这就是 TSMC 如何在 IEDM 上推出世界上最先进的逻辑技术的一些细节。

资料来源:

https://semiwiki.com/events/351309-tsmc-unveils-the-worlds-most-advanced-logic-technology-at-iedm/#comment-44032