荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

来源 / Semiconductor Engineering,内容有删减 作者 / GREGORY HALEY

检测 5nm 以下的缺陷给芯片制造商带来了巨大的挑战,这些挑战直接影响良率、可靠性和盈利能力。除了更小、更难检测之外,缺陷通常隐藏在复杂的器件结构和封装方案之下。

目前,半导体行业正在向创新的、数据密集型的检测方法过渡,这些方法能够使这些埋藏的缺陷可视化。先进的电子束 (e-beam) 检测、增强的 X 射线断层扫描和人工智能 (AI) 驱动的分析对于这些极端节点的缺陷检测变得至关重要。

图片来源 / 豆包

Part 1

AI 正在改变缺陷检测

晶体管架构(如全环绕栅极 (GAA) FET 和 CFET)以及 3D-IC 等新封装架构的演变大大增加了发现缺陷的难度。其中许多缺陷隐藏在多层堆栈深处或复杂的互连方案之下。这使得检测和缺陷表征变得更加困难,因为传统的电气测试和目视检测难以穿透和解释深层嵌入的缺陷。

鉴于X射线计量技术具有无损可视化内部结构的固有能力,因此越来越多地采用 X 射线计量技术来检测埋藏缺陷。然而,即使是 X 射线技术在接近 5nm 以下尺度时也面临分辨率和通量方面的限制。

在这些尺度上,看似微不足道的缺陷(混合键合界面中的原子级空隙或纳米级互连中细微的线边粗糙度)会显著降低器件性能。针对较大几何形状进行优化的传统计量工具通常会忽略这些微小但关键的变化。因此,这种情况不仅需要逐步改进,还需要全新的检测方法。

“干涉测量法仍然在晶圆计量学中占主导地位,但它也有局限性,尤其是随着封装技术的发展,”Wooptix 首席运营官 Javier Elizalde 说。“我们现在看到对能够适应新材料、新粘合方法和新工艺流程的替代测量方法的需求不断增长。”

为了解决这些限制,公司正在将高分辨率成像与 AI 驱动的数据解释相结合。例如,电子束检测正在得到重大改进,特别是通过冷场发射 (CFE) 源的发展,显著提高了分辨率和检测速度。

“先进节点面临的一个基本挑战是平衡检测速度和分辨率,”应用材料公司电子束缺陷控制营销主管 Ran Alkoken 说。“我们的第二代 CFE 技术在不牺牲分辨率的情况下显著提高了电流。这对于管理在这些高级节点遇到的密集缺陷图至关重要。

AI 驱动的分析在改进缺陷分类方面也发挥着至关重要的作用。通过在包含仿真和真实设计数据的广泛数据集上训练模型,这些算法大大减少了误报,简化了检测工作流程,并提高了缺陷检测的准确性。

“基于 AI 的检测不仅提高了吞吐量,”Alkoken 说。“它显著减少了误报并简化了缺陷分档。在生产晶圆厂中,由于这种功能,人工审核工作量减少了 50% 之多。

这些进步凸显了集成缺陷检测策略的更广泛趋势,利用 X 射线、电子束和 AI 等多种模式来确保在先进半导体节点进行有效的缺陷检测。

“许多团队仍在使用菊花链和连续性测试,这些测试会遗漏细微的故障,”Lewis 说。“这是一种老派的心态。他们正在测量只能检测粗略包装缺陷的东西,希望能检测出细微的包装过程问题。这些传统方法无法测量工艺异常值,这可能会在大批量爬坡中扼杀您的初始产量,直到检测到并纠正工艺问题。

随着晶体管密度的增加,细微的缺陷特征通常会与正常的工艺变化或背景噪声混合。机器学习 (ML)在海量数据中识别有意义模式的能力现在是将良率保持在 5nm 以下的核心。

“低于 5 nm 的结构复杂性使缺陷检测变得非常复杂,”Levin 说。“如果没有 AI 算法,传统的 X 射线断层扫描很快就会受到限制。AI 有助于从密集的衍射数据中提取有意义的信号,准确识别传统方法可能忽略的细微缺陷。

AI 显著提高了缺陷分类的可靠性,有效地将良性特征与关键缺陷分离,并大大增强了良率管理。随着半导体制造转向更复杂的结构,例如基于小芯片的架构和堆叠晶体管,这一点尤为重要,这些结构经常出现埋藏缺陷并且难以隔离。

“AI 显著提高了缺陷分类的效率和准确性,实现了更快、更可靠的晶圆检测,”Alkoken 说。“这不仅提高了吞吐量,而且显著减少了人工审查,使工程师能够腾出时间来解决影响产量的关键问题,而不是常规分拣。”

Part 2

先进封装是新的缺陷前沿

先进封装技术,包括混合键合、3D 堆叠和扇出晶圆级封装 (FOWLP),正在显著改变半导体制造。虽然这些方法提供了关键的性能优势,但它们引入了复杂的新缺陷机制,传统检测方法难以有效解决。

该行业向异构集成和超精细互连间距的转变放大了检测多层结构深处缺陷的挑战。随着先进封装的采用,准确识别和表征关键接口、硅通孔 (TSV) 和再分布层 (RDL) 的缺陷对于确保器件可靠性变得至关重要。

混合键合是这些挑战的缩影。该工艺对于实现超高密度芯片集成至关重要,需要近乎完美的表面平整度和原子级精度。即使地形的微小变化或键合界面的轻微污染,也可能导致键合缺陷或电气性能下降。因此,对专业检测技术的需求越来越大,这些技术可以在最终集成之前准确测量晶圆平整度并检测微观变化。

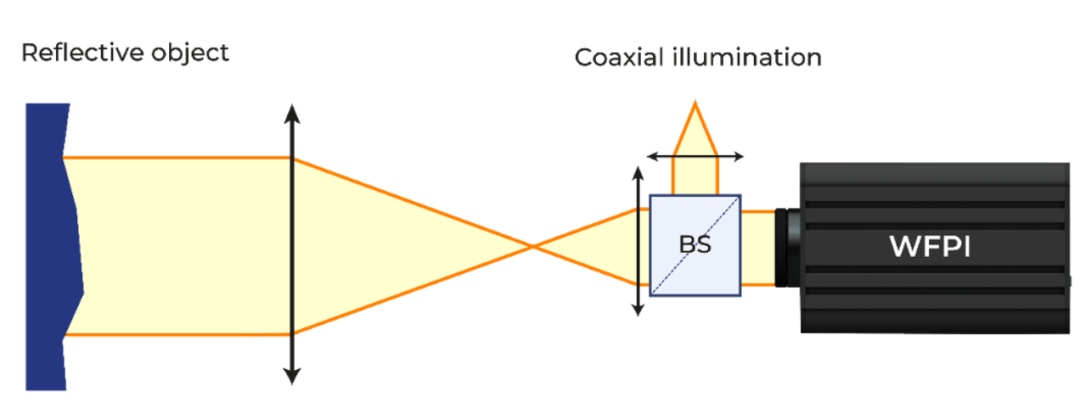

例如,Wooptix 的波前相位成像 (WFPI) 源自天文学中使用的自适应光学器件,它使用标准图像传感器从两个不同的焦平面捕获强度数据。

与需要参考光束的干涉测量不同,WFPI 直接从这些强度变化中推断相位信息。这使得系统能够以亚纳米垂直分辨率和微米级横向分辨率重建表面拓扑的详细相图,从而有效地检测前端工艺晶圆和后端的先进封装。

图 1:WFPI 可在一次 0.1 秒的拍摄中对 300mm 晶圆进行全场成像,收集数千万个测量点。资料来源:Wooptix

“确保晶圆平整度对于成功的混合键合绝对至关重要,”Elizalde 说。“传统的干涉测量方法根本无法达到先进封装所需的精度水平。我们的波前传感技术以亚纳米级精度提供实时平面度测量,使制造商能够及早纠正变化,并在后期避免代价高昂的缺陷。

此外,TSV 和 RDL 的完整性(各种 3D 配置和 FOWLP 结构中的关键要素)已成为一项主要的缺陷管理挑战。传统上用于整体器件的电气测试经常无法识别这些埋地结构中的缺陷。由于不透明材料层下的可见度有限,光学检测也难以实现,这推动了该行业转向能够无损可视化内部包装结构的先进 X 射线断层扫描和电子束显微镜解决方案。

布鲁克最近在 X 射线断层扫描方面的改进说明了工具制造商如何应对这些挑战。该公司的高分辨率 X 射线系统现在经过专门调整,可检测细微缺陷,例如 TSV 中的微空隙和 RDL 中的轻微不规则性,这对于保持多晶片封装的结构和功能完整性至关重要。

“在后端,有一种推动力来表征较轻的元素,”布鲁克的 Levin 说。“关键互连中的微空隙等问题对整体设备性能有着巨大的影响。高分辨率、AI 增强的 X 射线断层扫描已成为准确识别这些内部异常不可或缺的工具,使制造商能够提高产量并加强过程控制。

先进封装引入了结构缺陷以及与信号完整性、阻抗不匹配和电磁干扰 (EMI) 相关的新类别功能缺陷。随着包装密度的增加,即使是微小的结构缺陷也可能导致仅靠传统物理检测无法检测到的重大功能问题。因此,全面的缺陷检测越来越需要集成结构检测、电气分析和高级仿真工具,以全面评估封装可靠性。

“在先进的前端工艺节点以及先进的封装中,即使在最高分辨率的显微镜下,缺陷也并不总是可见的,”PDF Solutions 现场资源副总裁 Michael Yu 说。“将 X 射线、电子束、光学和电气测试与 AI 驱动的数据分析相结合的综合检测方法现在至关重要。您不能依赖单一工具;整体方法是必要的。

Part 3

克服行业障碍,实现有效缺陷检测

虽然 AI 增强分析、电子束检测和 X 射线断层扫描方面的技术进步意义重大,但多重实际障碍仍然阻碍着整个半导体制造生态系统的广泛采用。可扩展性、标准化和数据集成方面的挑战仍然是从被动缺陷检测方法过渡到主动和预测性策略的重大障碍。

此外,可扩展性是一个关键障碍,尤其是对于较小的晶圆厂和代工厂。虽然领先的制造商对最先进的检测解决方案进行了大量投资,但小型或专业化的晶圆厂经常发现这些工具在经济上无法获得。这种经济差距限制了整个行业更广泛的采用,并有可能造成不公平的竞争环境,即较小的晶圆厂难以在先进节点上进行有效竞争。

标准化是另一个主要障碍。随着从小芯片到预集成多晶粒模块的新型半导体结构的激增,其中一些还采用了特殊材料,各种独特的检测挑战成倍增加。这种多样性使得标准化检测方法特别具有挑战性,可能导致缺陷管理方法分散。

最后,芯片制造产生的数据量对分析能力提出了很高的要求。强大的集成平台对于跨生产阶段捕获、分析和安全地共享数据至关重要。虽然 AI 驱动型方法带来了巨大的前景,但它们的成功取决于无缝的数据通信和全面的分析基础设施。

应对这些挑战,实时分析和集成的生命周期缺陷管理正在成为在良率和可靠性问题蔓延到下游之前主动缓解问题的关键策略。

Part 4

结论

随着半导体制造深入到 5nm 以下领域,缺陷检测已从一个简单的制造步骤迅速演变为保持良率、可靠性和竞争优势所必需的战略能力。传统的检测方法很快就会达到极限,这要求制造商和设备提供商积极创新。

先进的电子束检测、增强的 X 射线断层扫描、波前相位成像和 AI 驱动分析的集成代表了向前迈出的重要一步。然而,要充分发挥这些技术的潜力,关键取决于解决可扩展性挑战、标准化差距和数据集成复杂性。

原文链接:https://semiengineering.com/nearly-invisible-the-future-of-defect-detection-below-5nm/

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。