荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

在2.5D和3D-IC中,温度完整性变得越来越难以准确预测,而这将导致一系列问题,包括影响系统运行到现场可靠性等所有方面。

在过去十年,硅中介层技术已经从一个简单的互连技术发展为异构集成的关键组成部分。目前的中介层可能包含有数十个芯片或芯粒(chiplets),以及数百万个连接,并且对性能、功耗和面积的要求也不断提高。事实上,在面积超过2000平方毫米的中介层上进行异构集成设计已并不罕见,该系统需要消耗600瓦的功耗,并且需要非常高的I/O带宽。达到如此高的功耗,首先就需要关注温度完整性,否则工程师将很难放心地按时完成signoff。

目前已经有许多工具可以用来了解和建模异构硅中介层设计中的热效应问题,但大多数工具都是不互通的。虽然应用这些工具进行了建模,但还不能完全解决问题。因为目前还不清楚这些工具到底应该做什么,以及所有的零部件到底是如何组合在一起的。

4月28日,荣格“先进封装技术论坛”线上直播将举办,更多有关封装技术的分享,请扫码预约观看。

Synopsys杰出架构师Rob Aitken表示:“我们目前面临的普遍挑战都是从这个观念产生的,即‘假设这些东西都是很小的板,我们会采用在板级和封装级时应用的相同技术,只需要缩小尺寸就可以了。’某种程度上这是对的,但它有几个新的维度。首先,现在做这件事的人与过去的不同。以前是封装和电路板工程师需要做建模,现在芯片人员也在做这件事情。”

还有其他的重大变化。西门子数字工业软件Calibre接口和EM/IR产品管理资深总监Joseph Davis表示:“在进行这些3D组装时,需要记住的是,我们涉及的领域与过去不同了。过去芯片人员负责将芯片进行封装,然后我们有了两个新的选择——系统级封装和MCM。许多界线都已经模糊了,到底谁需要做什么?封装人员在做封装和系统模拟。对他们来说,整个芯片都有温度,因为他们是以厘米级的分辨率来观察板上或封装中的散热情况。

而IC团队,他们现在也不仅仅需要处理一个IC,而是有许多个IC叠加。IC团队则是以微米级的分辨率进行观察。他们需要知道整个IC内的温度分布情况等等。分辨率成为一个挑战。实际上,物理和技术问题是最容易解决的部分。真正的问题是,每当需要跨部门合作时,才会遇到真正的问题。我们现在正在将多个芯片组合在一起,这些芯片有时可能采用不同的技术,有时来自不同的代工厂。即使来自同一个代工厂,每个芯片堆叠的方式也都是独一无二的。目前还没有一个能涵盖所有这些信息的工具。”

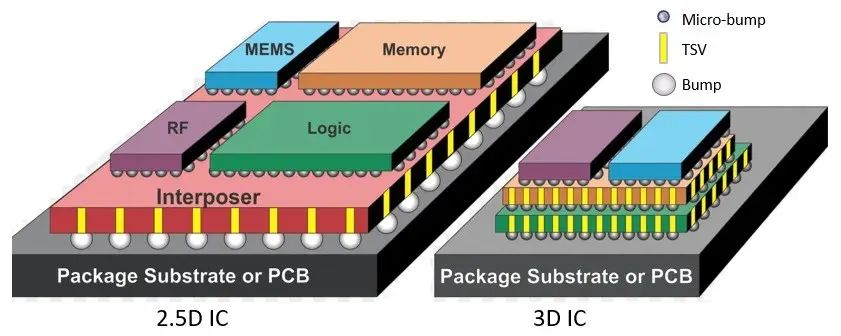

图1:使用中介层、凸块、微凸块和硅通孔的先进封装(图源:西门子)

要做到这一点,各方之间必须进行沟通——包括芯片设计公司、EDA工具厂商、代工厂和封装厂。

Davis说道:“即使是同一家代工厂,我们都必须弄清楚所有需要考虑的问题,并把所有东西都准备好。而封装和系统人员是以毫米级进行观察思考的。因此,有两个非常不同的用户群,每个用户群以不同的分辨率工作。”

并且,间距和互连也不同。Synopsys的Aitken表示:“尤其是硅中介层,需要处理不同的材料。一块电路板和一块有机基板从材料上来说是相似的,所以对于过去在电路板上适用的所有做法,通过设计一块测试芯片来测试这个系统的极限。如果这些都能通过,那就太好了,但没人能确定它们能持续多久。物理就是物理,但它会改变。如果不够小心,过去是二阶效应的东西可能会变成一阶效应。”

从头开始改变

一个典型的异构集成系统都是逐步构建而成的。

Ansys首席产品经理Lang Lin表示:“从系统的封装基板开始,我们实际上在其顶部集成了中介层,并有数十万个凸块进行连接。根据设计集成计划,设计师会直接在中介层顶部增加几个芯片或芯粒。一些芯片通过微凸块或铜-铜连接进行互连,另一些芯片可以通过3D方式进一步堆叠。由于这种集成方式,中介层的作用就是可靠地将数百万个这样的微凸块进行连接或采用铜-铜连接,使整个系统能够运行。”

这通常被称为芯片封装系统。中介层是一个桥接器,它包含了所有零件的电力传输网络。Lin表示:“它还为所有的芯片和芯粒提供电源,并管理所有芯粒和芯片。但目前封装在顶部的芯粒会消耗大量能量,这可能会导致电源完整性问题,而且在工作时也会产生大量热量,因此会出现这样的状况,一块IC有可能因温度完整性问题而烧毁其相邻的IC。”

简单地说,异构集成可能会导致电源和温度完整性问题,甚至更多其它问题。

Lin说道:“如果你的产品是具有高带宽内存的3D堆叠芯片,那么功耗和热问题也可能导致严重的信号完整性问题。这意味着异构集成系统中会同时出现这些问题。设计师需要在确保功率成功传输、热量成功耗散的同时,也要保证信号完整性不受影响,这非常重要。”

对基于中介层的异构设计进行建模会对模型的完整性有疑虑,因为涉及的变量太多了。Lin表示,“假设在某些条件下,比如,‘一种材料对另一种材料的偏转是线性的。’然后又会说,‘事实上,在其他一些条件下,它是二次的。’但二次模型要复杂得多。应用使用哪一个?业界仍在寻找答案。”

这在很大程度上是抽象级的函数。Davis指出,所有这些热问题都可以通过非常粗略的建模和平均值来解决。他表示:“有了新技术和这些技术的混合,我们在系统中有了很多非常好的绝缘体。但当我们使用finFET时,情况变得更糟了。人们开始意识到,‘发热问题更严重了。’为什么会这样?’这是因为对于平面晶体管,所有的热量都在硅中产生。块状硅是很好的热导体。它的热导率约为150。有了鳍后,上面也可以集成晶体管,它被二氧化硅隔离,二氧化硅是一种非常好的绝缘体,它的导热系数是1.4,所以有100倍的差值。稍等,我们刚刚是把发热晶体管包在一个玻璃枕头里了吗?那该怎么处理产生的热量呢?得想办法把它们散出去。这是通过TSV等技术来完成的。此外,我们也可以对此建模。我们每天都通过模拟和EM/IR对比发热更复杂的情况进行建模。我们当然有这样的能力。但将所有数据汇总是一个真正的问题。最大的问题就是系统中的分辨率,且这个系统不是电子系统,是工业系统。”

Aitken则表示,可以从两个方面看待该问题。“一方面,‘我有一个系统,我有一堆在建模系统时使用的方程式,我也有实现这些方程式的工具。’然后我得到输出结果。输入部分也非常重要,因为所有的芯片都不一样。所有的材料也都可能略有不同。此外,工作负载不同,有时还是未知的,所以,再强调一次,你需要处理我们一直在封装上和芯片设计上需要考虑的热问题,但现在它们混合在了一起,不能再单独视之,这导致需要做尽可能多的分析。”

了解热流也至关重要。热量从物体较热的一端移动到较冷的一端,但也并不总是这样。“热传导的概念很容易理解,”Ansys的Lin表示,“如果你了解欧姆定律,你就知道可以用等效热阻来建模系统的热传导路径。给定一个特定的功率耗散值作为这个系统的热沉,你就可以很容易地解决传导路径两端之间的温差。傅立叶热传导定律描述了系统如何散热,以及热沉如何影响整个系统的温差。”

通过硅中介层映射傅立叶定律更为复杂。“假设一个芯粒中有两个热源,”Lin说道,“这个硅系统的芯粒耗电,而中介层封装在顶部。系统中总共可能有四个不同的零件或组件。我们可以对四个零组件的热阻进行建模。考虑到两个芯粒正在让系统变热,我们有两个Q(热流)源,将热量注入热传导路径。”

解决这一问题可以帮助设计者了解系统每个零组件之间的温差,从而更好地了解温度分布。但Lin表示,这个模型还不够准确,因为每个零组件只有等效的热阻。“热阻实际上高度依赖整个组件的材料属性。有限元分析方法可以用数学方式表示具有自身材料特性的物理零组件或系统,以及所有界面的边界条件。网格技术用于将IC layout几何体或物体转换为可识别的元素。使用两个不同的网格方法可以对整个IC layout进行建模,然后使用所有网格元素,可以以3D方式了解系统所有元素之间的热传递定律。”

这也有助于解决温度分布问题,这是一个现实问题,需要更准确的散热模型。

考虑到网格划分如何影响解决热传导的精度,Lin表示,网格划分技术还需要不断改进,这也是一项挑战,因为从之前的SoC技术转换到最新的2.5D或3D-IC技术,系统变得越发庞大。在这些复杂的系统中包含了数以万计的热源。因此,网格的分辨率也必须从厘米级提高到微米级,甚至是纳米级。“我们需要一个更小粒度的解决方案,至少需要达到集成芯片子模块级别的大小,这样我们才能准确地对热传导路径进行建模。这非常具有挑战性,但这是解决此类系统热节流问题的必要条件,以确保不存在可靠性或热完整性问题。”

分而治之的方法显然已经不适用。西门子数字工业软件产品管理总监John Ferguson指出,从历史上看,热能问题是通过网格方法解决的。“将东西分成小方块,然后能达到的效果取决于有多少硬件、内存,以及等待的时间。这些都是需要努力解决的问题。但这种网格方法还有另一个挑战,即温度本身。”

革命性改变

这个领域的解决方案最终会是什么样子,还有待观察。Aitken指出,目前已经进行了广泛的板级实验,相信在某些时候,这个行业将开始合并。Ferguson说道:“即使从封装方式来看,过去的封装方式数量很少,而且这些封装分类也是因为封装供应商不同所致。但现在有很多不同的封装设计,即使只限于硅中介层,它们的应用也很多样,也有很多方法将它们组合在一起。哪一个更好,业界还没有达成任何共识。这意味着制造商必须支持定制化的产品,不仅针对每个客户,而且可能针对每个设计。

此外,在早期做出决策也是一个挑战。

西门子公司的Davis表示:“我们询问架构师什么可以组合在一起?封装足够大吗?热沉足够大吗?一直以来行业处理这一问题的方式是预算和近似模型,所以当需要更快、更早地设计系统,则需要模型。有时模型只是一个近似值,‘我认为这个芯片会产生这样的温度,因此它会这样传导。’但现在我们看到客户在问,”我设计了这个部分,并将其封装。新的设计将有一些额外的驱动程序,预计会产生很多热量。封装够了吗?在开始影响可靠性之前,散热是否足够?’在谈到其他问题之前,必须先解决这些问题。电迁移是温度的函数,所以如果温度(指数函数)比预期的高10度,它可能会使设备的寿命缩短5年。工程团队希望早点解决这些问题,但他们不了解他们将使用何种技术,只能说,‘我们正在考虑这个问题。’”

结语

可以肯定的是,如果设计师意识到所有这些挑战,他们现在有一些技术可以应用。但在复杂异构设计中有很多元素需要考虑,这对设计团队来说是一个更大的挑战。

“他们可以从设备层面应用几种不同的解决方案,”Lin说道,“他们可以降低功耗,平衡功率密度,并可以巧妙地划分芯片和芯粒,使热传导路径保持良好平衡,不产生任何高温。在系统级层面,我们看到有很多冷却解决方案,‘如果温度太高,就对系统进行节流,使其无法工作,然后让它休眠。’也可以实施如热管理、电液体冷却和强制对流等其它手段。这些系统生产中都已存在。”